Table Of Content

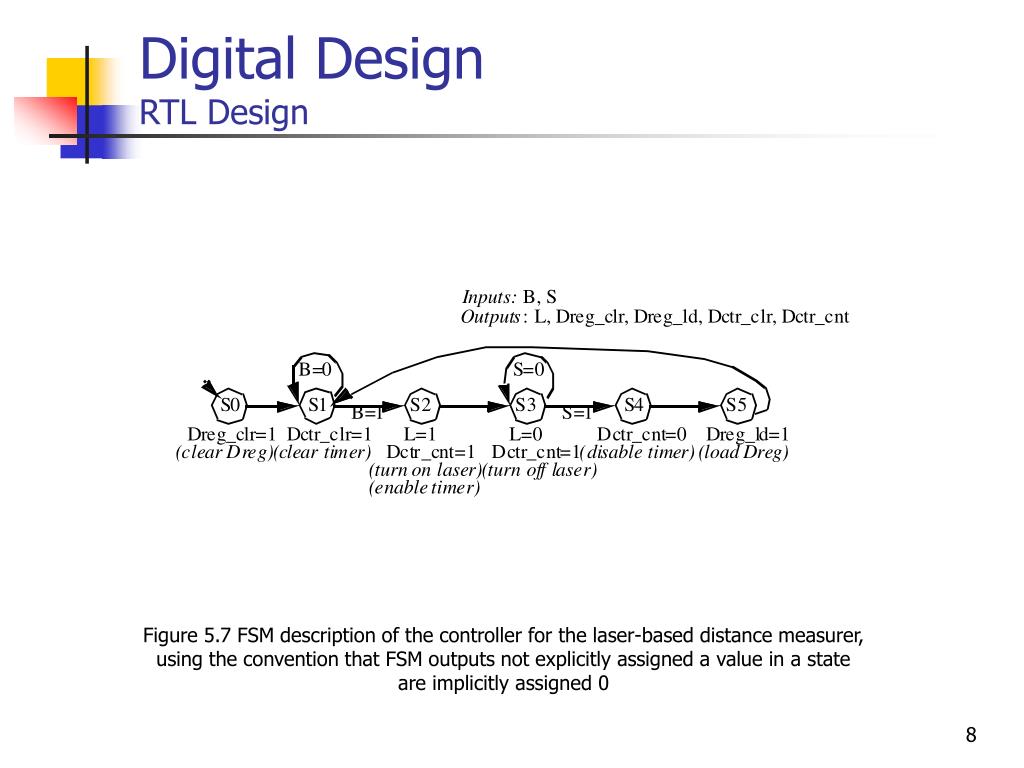

Post-simulation, the RTL design is synthesized into a gate-level representation. This synthesis involves converting the high-level HDL description into a network of logic gates. The synthesized design is then verified against the original RTL to ensure accuracy. RTL design begins with defining the functionality of the digital system in an HDL. This definition includes specifying how data is processed and transferred in response to inputs.

The Basics of RTL Design

This gate-level netlist is then used for physical design and manufacturing processes. Next, the RTL description of the DSP system was written using a hardware description language, such as VHDL or Verilog. The RTL description defined the data paths and control logic of the DSP system, including the registers, arithmetic units, and control units. However, due to the exponential growth of the state space with the size of the design, it is impossible to simulate all possible input vectors for large designs.

FireSim: FPGA-Accelerated Cycle-Exact Scale-Out System Simulation in the Public Cloud

This work presents the generator of high-fidelity, runtime-reconfigurable, last-level cache and DRAM timing modelsprovided by MIDAS and used in FireSim. If your company is looking to recruit highly skilled engineers worldwide, contact us today and we will do the sourcing for you. Or if you’re an engineer looking for new opportunities, you can check RunTime Recruitment’s job site for job vacancies.

Timing Analysis and Optimization

By using simulation and formal verification methods, designers can confidently verify the correctness of their RTL designs and proceed to the next stages of the design process. Founded in 2005 and based in Los Angeles, DKNG is a full-service design studio mainly serving the music and entertainment industries. The company provides graphic design services, including identity development, traditional print media, and packaging, apparel, and web design. Its team of designers creatively combines color, typography, photo, and illustration to provide high impact designs on posters, T-shirts, products, and icons. RTL design and gate-level design are two levels of abstraction in the design of digital systems. RTL design focuses on the data paths and control logic of the system, while gate-level design focuses on the implementation of the system using logic gates.

Do I need a degree to be a graphic designer?

Verilog code is typically organized into modules, which define both the interface and behavior of a part of the system. During RTL coding, the designer writes the HDL code that describes the system's registers, operations, and data flows. This code is typically organised into modules, which are reusable blocks of code that represent specific parts of the system. Modules can be instantiated multiple times within a design, allowing for efficient reuse of code and simplification of the overall design. HLS tools, such as Cadence Stratus or Synopsys' Catapult, automate this process, allowing designers to quickly and accurately generate RTL descriptions from high-level system descriptions. [4] These tools also provide optimization features that can improve the performance, power, and area of the resulting RTL design.

For example, in a simulation of a 4-bit adder, the input vectors might be pairs of 4-bit numbers, and the expected output vectors would be the sums of these numbers. The simulation tool would apply these input vectors to the adder, observe the resulting output vectors, and compare them with the expected results to verify the correctness of the adder. Simulation tools, such as ModelSim or VCS, are used to perform RTL simulation. These tools execute the RTL code and provide a waveform view of the signals in the design, allowing the designer to visually inspect the behavior of the system.

After Nasdaq announcement: Chip designer Arm targets $52 bn valuation in year's largest IPO - RTL Today

After Nasdaq announcement: Chip designer Arm targets $52 bn valuation in year's largest IPO.

Posted: Thu, 14 Sep 2023 07:00:00 GMT [source]

By catching these issues early in the design process, linting tools can help improve the quality of the RTL code and reduce the risk of design errors. Given the complexity of modern digital systems, verifying that the RTL description accurately represents the intended behavior of the system is a non-trivial task. Errors in the RTL description can lead to functional errors in the final system, which can be costly to fix if not detected early in the design process. By using techniques such as RTL partitioning, high-level synthesis, and design reuse, designers can effectively manage the complexity of large designs and produce high-quality, efficient digital systems. RTL optimization is performed using RTL synthesis tools, such as Synopsys' Design Compiler or Cadence's Genus. These tools analyze the RTL description and apply various optimization techniques to improve the PPA of the design.

This involves writing the RTL code that describes the data flow and operations of the system, and optimising this code to meet the design requirements. RTL design focuses on the behavior of the circuit, whereas gate-level design focuses on the physical implementation of the circuit using logic gates. RTL design is a higher level of abstraction, allowing for easier design and modification, while gate-level design is more detailed and specific. The converters achieve high efficiency at the system level by switching simultaneously to avoid charge-sharing losses and by using an adaptive clock to maximize performance for the resulting voltage ripple. Details about the implementation of the DC–DC switches, DC–DC controller, and adaptive clock are provided, and the sources of conversion loss are analyzed based on measured results. In RTL design, the focus is on describing how data moves between registers (storage elements) and how it is transformed or processed in each step.

RTL Optimization

For example, in a microprocessor design, the processor core, memory, and input/output (I/O) interfaces might be separate partitions. The bests stage to timing analysis and quickly identify the path that causes timing problems is at the RTL level. Modern synthesize tools can perform the Static Timing Analysis (STA) of the design to find the potential timing issue that later causes the design’s metastability and negative slack. This article provides an overview of Register Transfer Level (RTL) Design, it describes the fundamentals of RTL design and the process of RTL design.

From Apple to Verizon, top-notch companies are fighting for the dominant spot in the market through their innovative and breathtaking products which can solve the pain points of the customers. Millions of dollars are being spent for R&D and simulation of building prototype models and RTL Designing plays a pivotal role in achieving that ambitious goal. With the modern and complex products thrown at us every day, it becomes quite a narrative for the product and innovation-led companies to come up with the best suited and tailor-made products for their respective target audience. But with all this hyped up, the inevitable question that pops up is how it is being evaluated, validated and what checks are being put in place. Our expert team of engineers-turned-recruiters offers in-depth knowledge of technical recruiting in the engineering industry.

It’s a field that combines creativity with technical prowess, continually pushing the boundaries of what’s possible in technology. In the ever-evolving landscape of digital electronics, RTL (Register-Transfer Level) design stands as a cornerstone, bridging the gap between theoretical concepts and physical hardware. This introductory article is dedicated to unraveling the basics of RTL design, its significance, and how it shapes the world of modern digital systems. This refers to the way in which the designer writes the RTL code, which can have a significant impact on the efficiency and performance of the resulting circuit. Good RTL coding style involves using clear, concise, and well-structured code, with a focus on minimizing the complexity and depth of the design. Verilog and VHDL are the two most used hardware description languages for RTL design.

Register-Transfer Level (RTL) design is a critical aspect of digital circuit design. It is a design abstraction representing how data flows between hardware registers and the operations performed on that data. RTL design approach is used in creating digital systems where the flow of data between registers, and the operations on that data, are important for the system's functionality. Synthesis is a crucial step in the FPGA design flow, as it plays a significant role in converting the RTL description of a digital circuit into a gate-level representation.

HLS offers several advantages, including improved design abstraction, faster verification, and the ability to leverage existing software development tools and methodologies. RTL design allows designers to describe the behavior of a digital circuit at a higher level of abstraction. It focuses on the flow of data and control between registers, enabling designers to express complex functionality concisely and structured. This behavioral description serves as a blueprint for the subsequent steps in the design process. RTL design is a hardware description method focusing on data flow between registers in a digital circuit.

It also includes the physical verification part of the chip, memory characterization, analog layout, and design. RTL design allows designers to optimize their circuits for specific goals such as power consumption, performance, or area utilization. By making changes at the RTL level, designers can achieve better results regarding power efficiency or speed [3].

Interfacing with AXI Peripherals in RTL - Hackster.io

Interfacing with AXI Peripherals in RTL.

Posted: Tue, 01 Mar 2022 08:00:00 GMT [source]

Our online Digital electronics course will help you to learn and refresh the complete fundamentals of digital electronics, which are highly needed for any VLSI course. Perfect for graphic designs with solid-colored elements like logos or vector illustrations. For over a decade, Print Renegades has been providing top-notch custom apparel printing services to satisfied customers in the Los Angeles area and beyond. We specialize in superior quality screen and DTG printing, embroidery, and similar customization services for a variety of items, such as t-shirts, hats, and posters. Count on us for fast turnaround times and exceptional results that will make you stand out.